Das CISPA Helmholtz-Zentrum für Informationssicherheit ist eine nationale Wissenschaftseinrichtung, die sich mit Informationssicherheit in allen Bereichen befasst. Im Rahmen ihrer Arbeit hat CISPA einen ASIC entwickelt, um zwei verschiedene Taktsignale zu synchronisieren, sodass sie frequenz- und phasenkohärent sind.

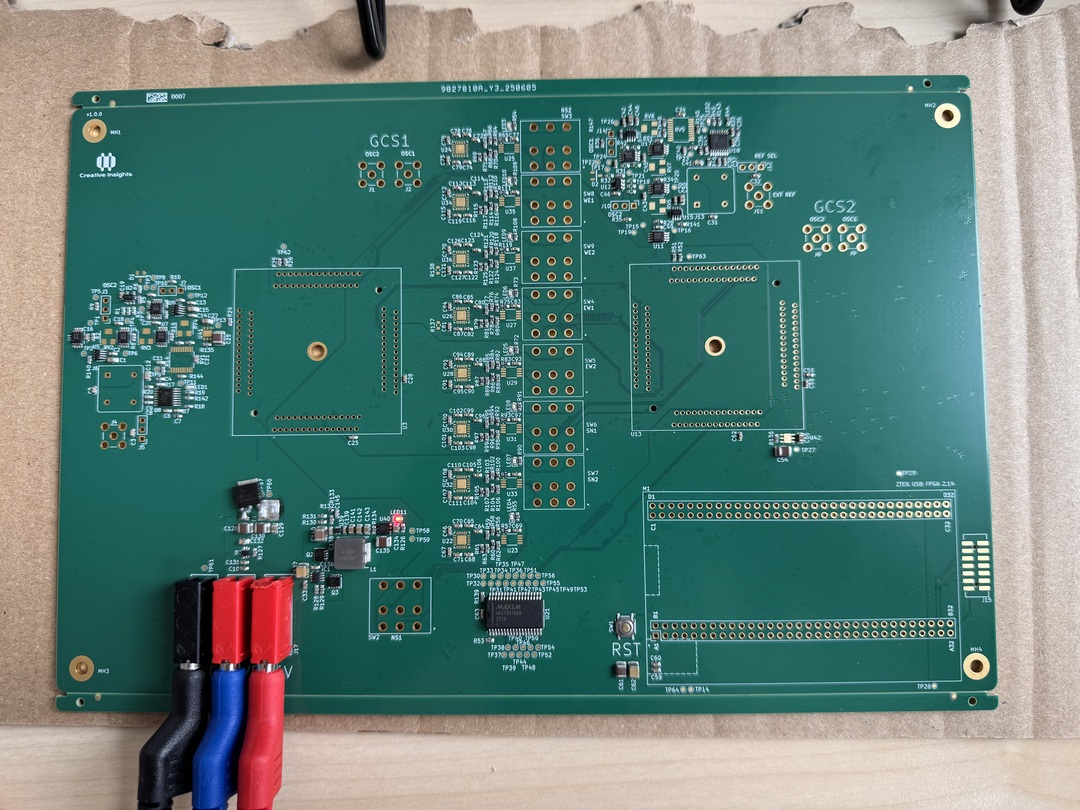

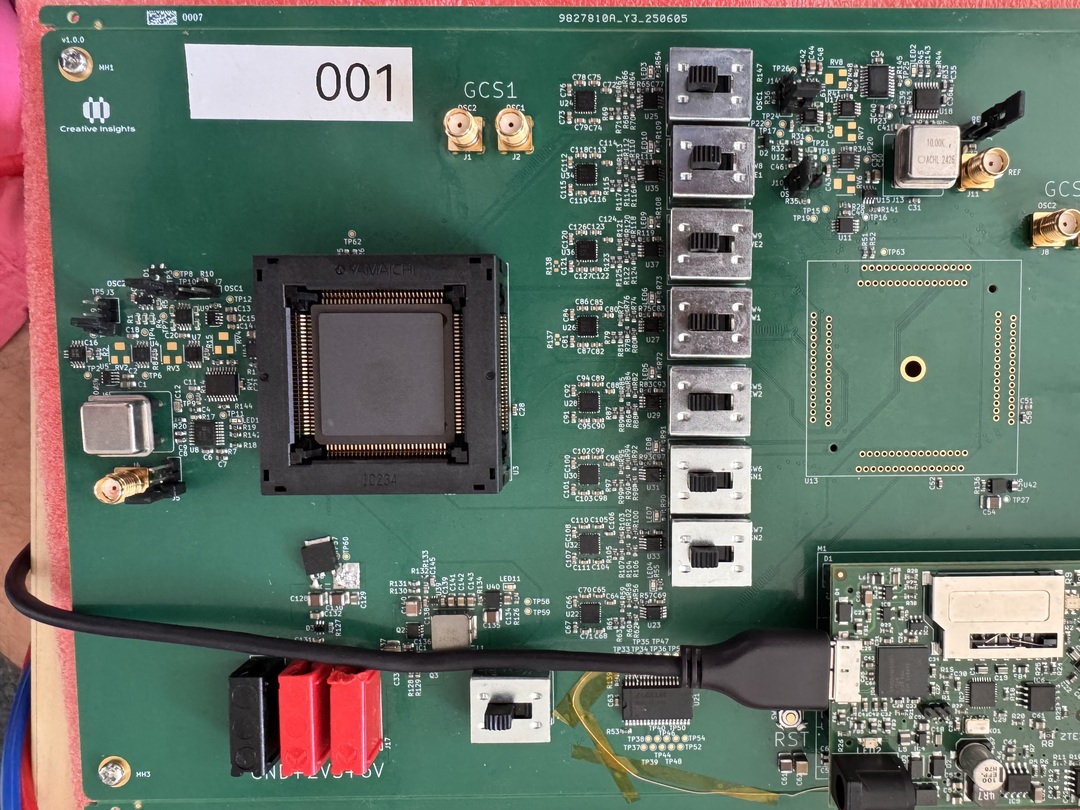

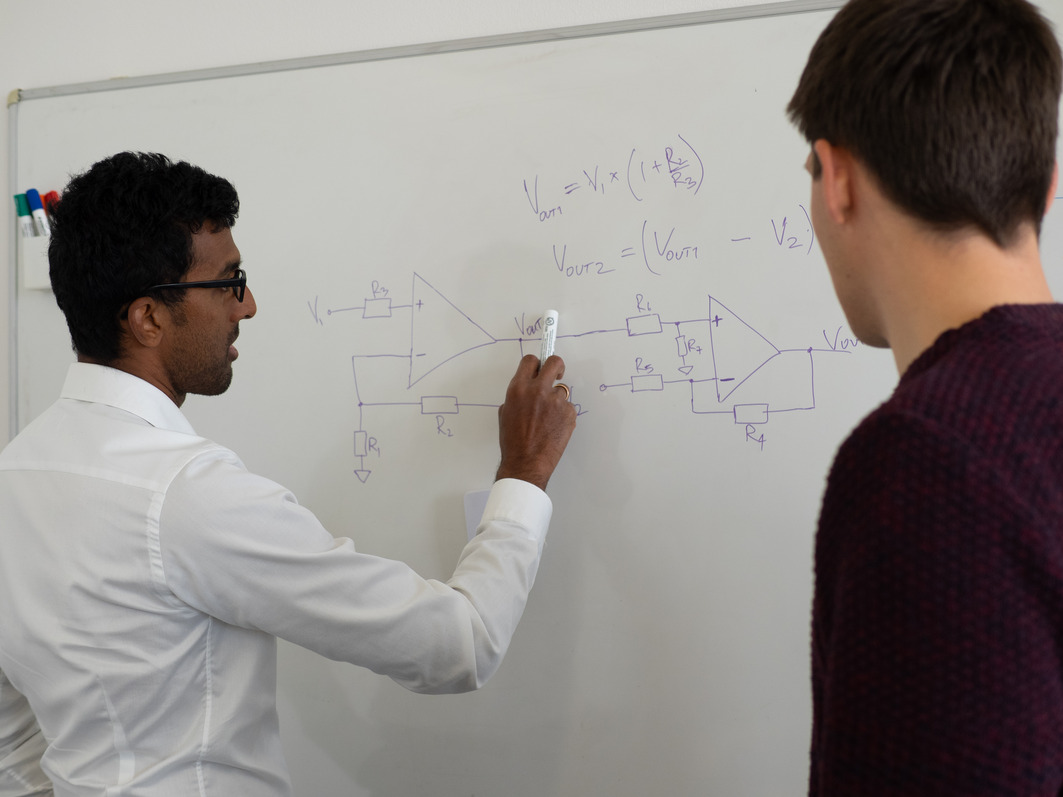

CISPA benötigte fachkundige Unterstützung, um ihren ASIC zu validieren. Mit unserer Expertise im Hochgeschwindigkeits-Design waren wir in der Lage eine Testleiterplatte zu entwickeln und bei den Post-Fabrication-Tests zu unterstützen, um die erfolgreiche Validierung der neuartigen Architektur sicherzustellen. Die Anforderungen waren wie folgt:

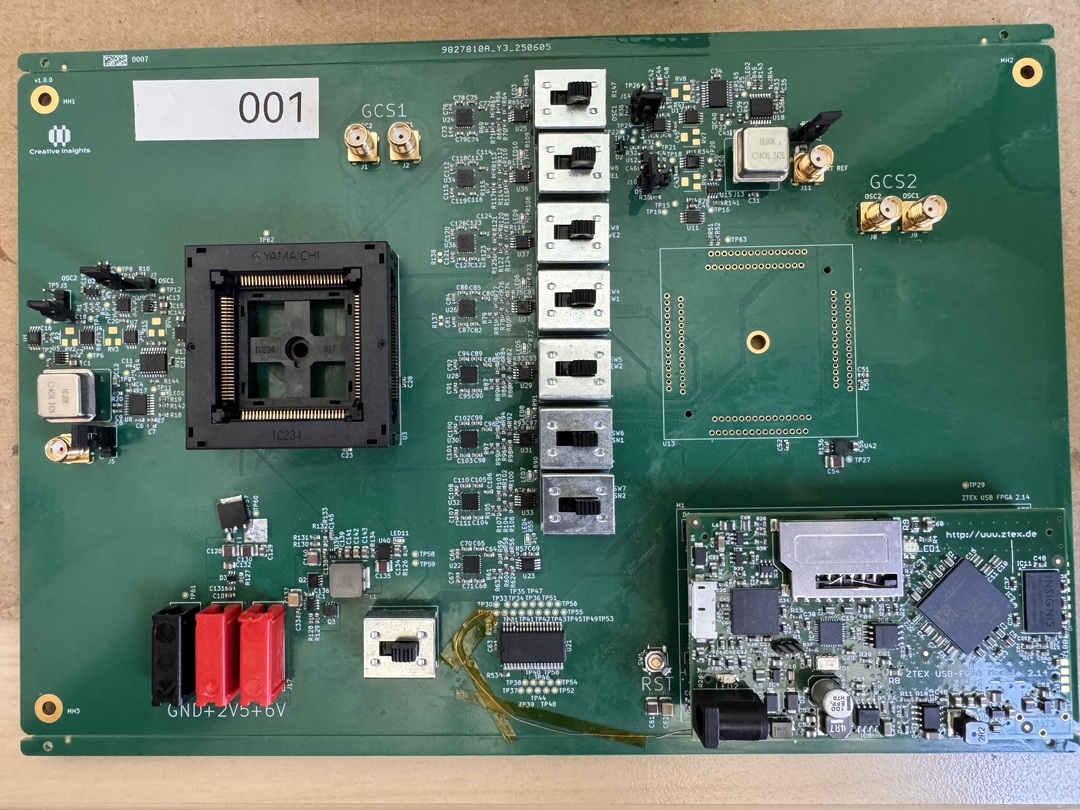

- Präzisions-DACs zur Steuerung von VCOs

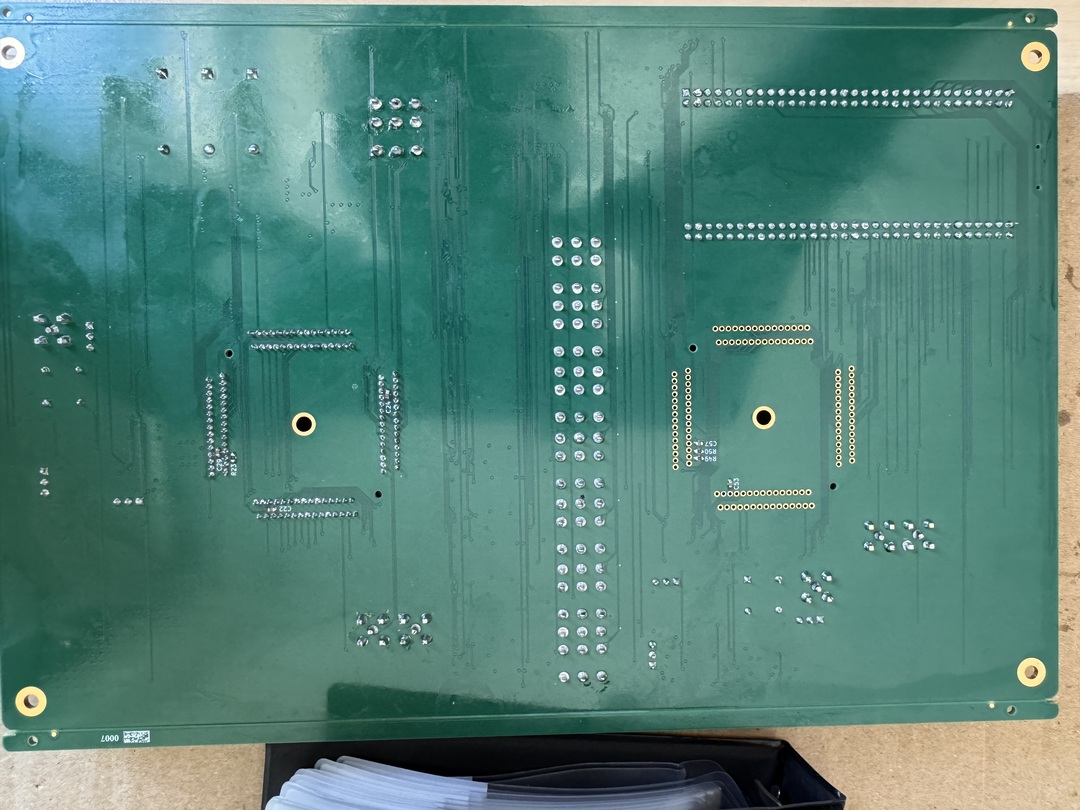

- Leitungslängenanpassung für zeitkritische Signalleitungen

- 1 Gbit/s Hochgeschwindigkeits-Datenübertragung zum Host

- FPGA für die Datenverarbeitung

- PLL-Chips zur Takterzeugung

- Multiplexing zwischen stabilem internem Takt und externer Referenz

Ergebnisse auf einen Blick

Geschäftsergebnisse durch hochqualitative Ingenieursleistung

Überprüfung des ERC-Projekts

Wir haben ein komplexes, mit 150.000 € ERC-Förderung unterstütztes Konzept in nur 3 Monaten in ein funktionierendes Board verwandelt. Ein Beweis für unsere Fähigkeit, Ideen schnell vom Labor auf den Markt zu bringen.

Präzises Timing

Synchronisation auf Nanosekundenebene durch sorgfältiges Trace-Matching und präzise DACs.

Schneller Datentransfer

Interne High-Bandwidth-LVDS- und PECL-Links sowie USB-C zum Host für maximalen Datendurchsatz während der Tests.

Komplexe Leiterplatte

Eine 8-lagige Platine mit FPGA, PLLs und Taktquellen, kompakt und anpassungsfähig.