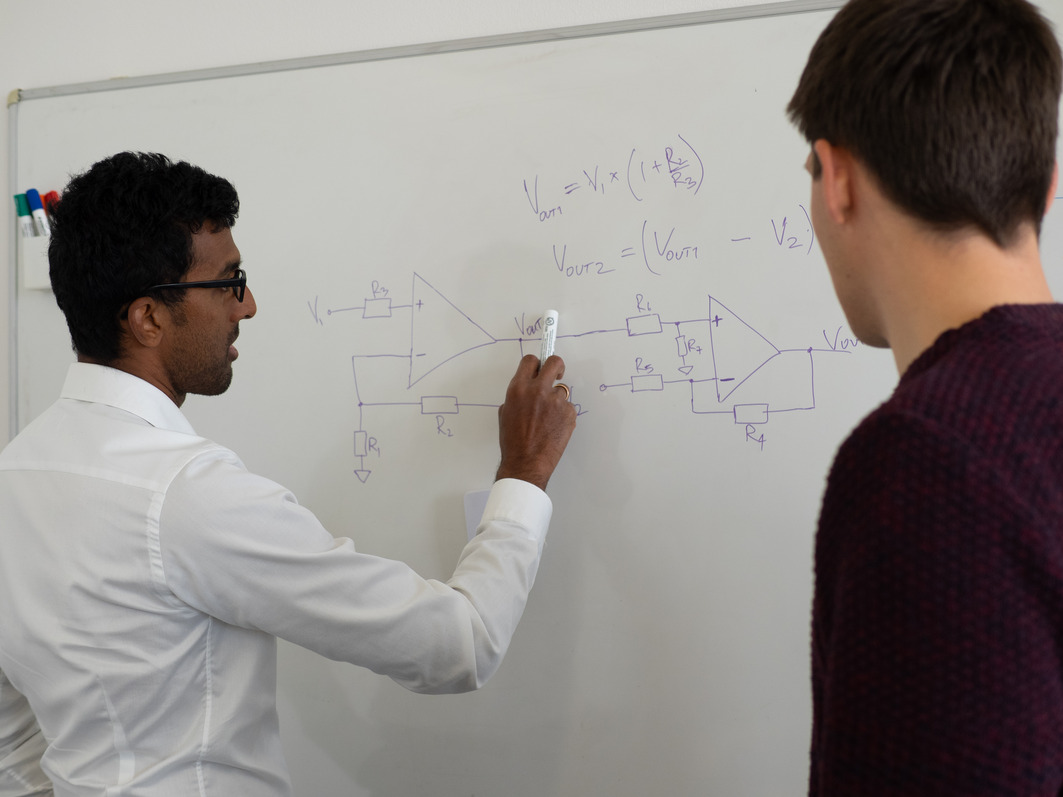

The CISPA Helmholtz Center for Information Security is a national science institution exploring information security in all facets. CISPA had developed an ASIC for the purpose of synchronising 2 different clock signals and lock them to be phase and frequency coherent.

CISPA needed expert support to validate their custom clock synchronization ASIC.

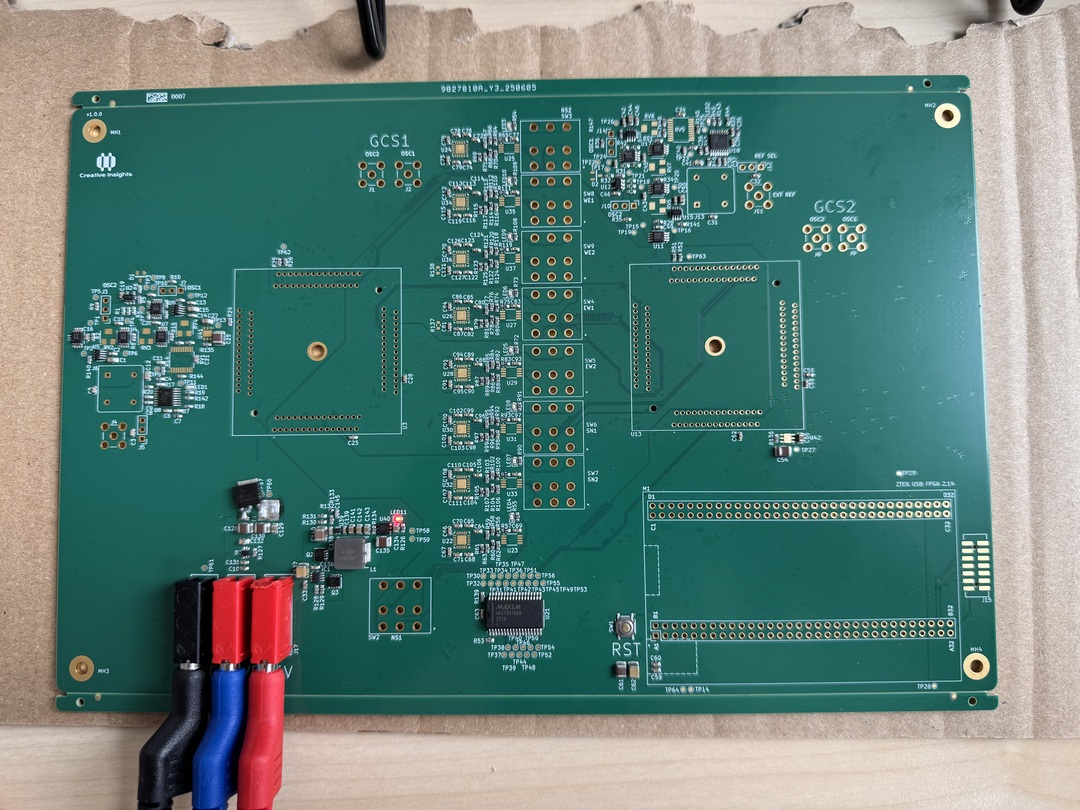

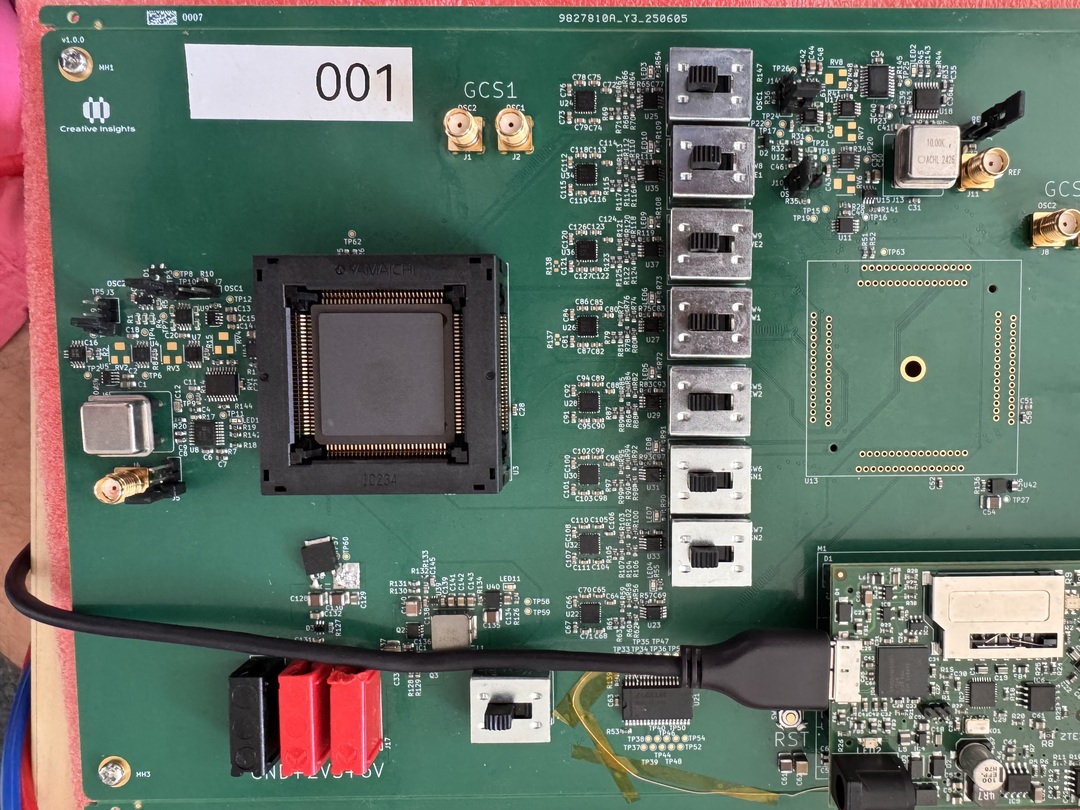

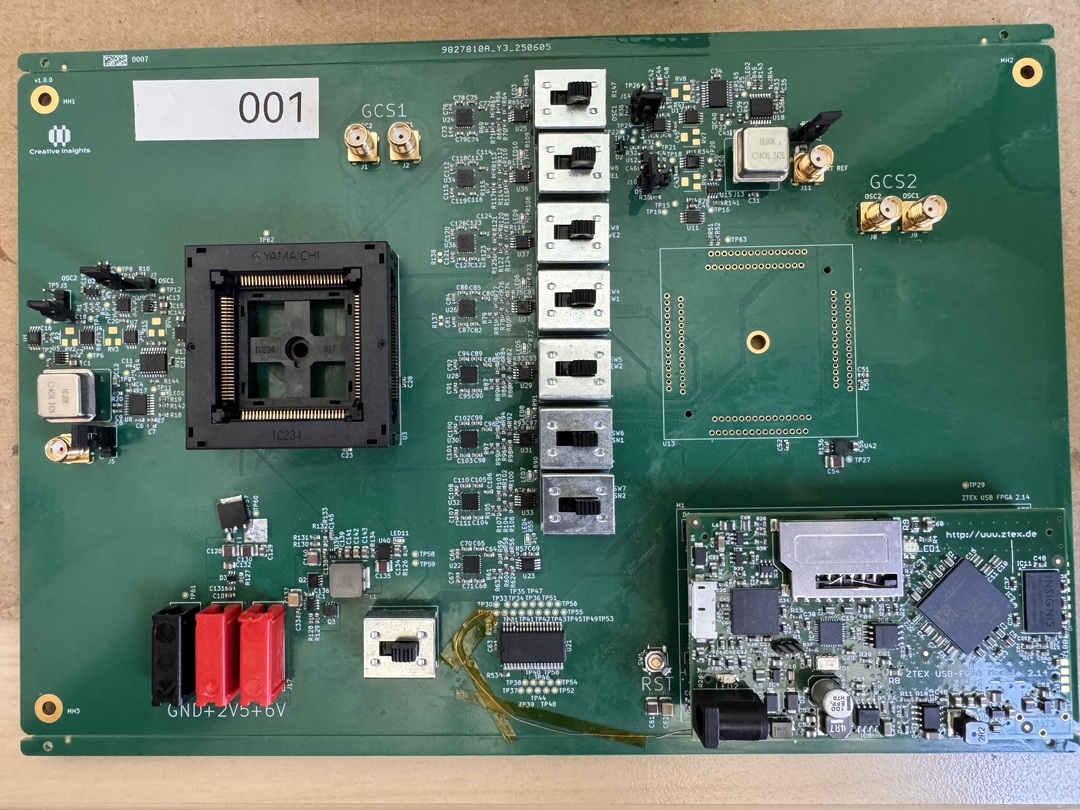

We brought in our high-speed hardware design expertise and collaborated on post-fabrication testing ensuring successful validation of their novel architecture. We delivered all the requirements which included

- Precision DACs to control VCO

- Trace length matching for time sensitive tracks

- 1Gb High Speed data transfer to Host

- FPGA for data processing

- PLL Chips for clock generation

- Multiplex between stable internal clock and external reference

Results at a glance

Business impact backed by engineering outcomes

Verification of ERC Project

We turned a complex, €150k ERC grant-backed concept into a working board in 3 months, demonstrating our ability to accelerate ideas from lab to market.

Precise timing on PCB

Nanosecond-level synchronization delivered through careful trace matching and precision DAC use.

Speedy data transfer

High-bandwidth LVDS and PECL links used internally and USB C used to the host, maximized data throughput during testing.

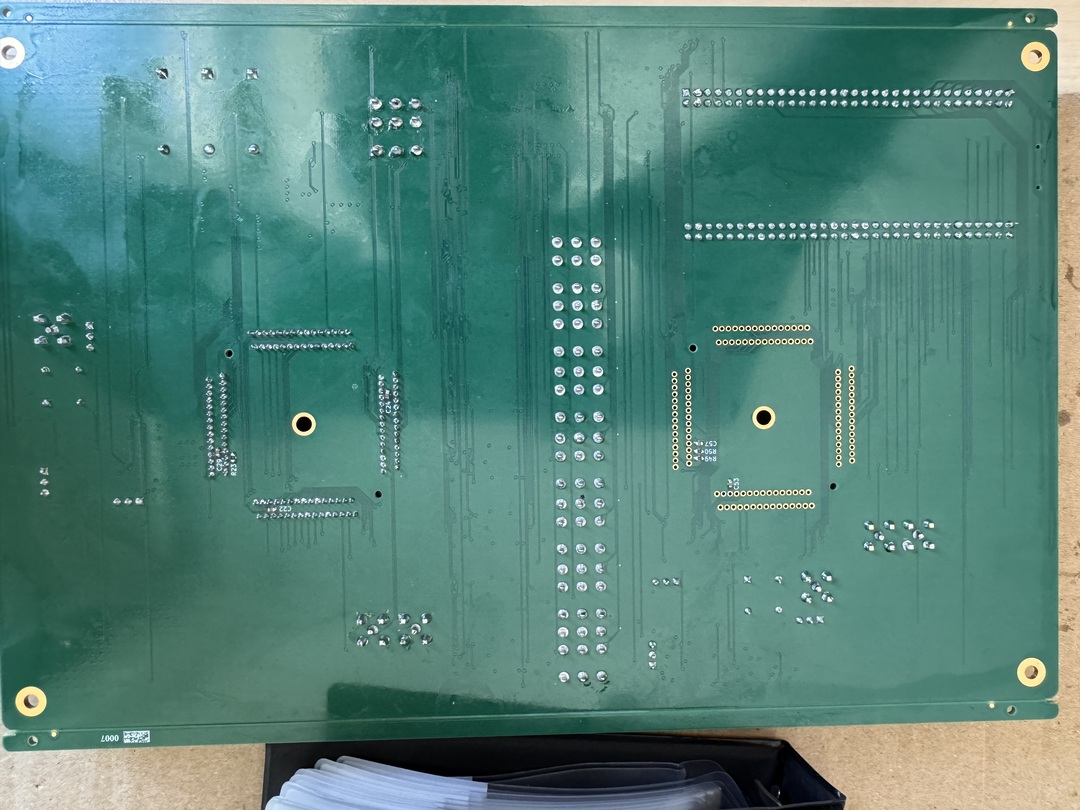

PCB complexity

An 8‑layer board with FPGA, PLLs, and clock sources, compact and adaptable.